# **DIGITAL** ELECTRONICS

# G. K. KHARATE

Principal Matoshri College of Engineering and Research Centre Nashik

# **C**ONTENTS

| Preface    |                                                | v  |

|------------|------------------------------------------------|----|

| Chapter 1: | LOGIC FAMILIES                                 | 1  |

|            | 1.1 Introduction 1                             |    |

|            | 1.2 Logic Families 2                           |    |

|            | 1.3 Transistor as Switch 3                     |    |

|            | 1.4 Characteristics of Digital ICs 4           |    |

|            | 1.5 Resistor-Transistor Logic (RTL) 8          |    |

|            | 1.6 Direct Coupled Transistor Logic (DCTL) 9   |    |

|            | 1.7 Diode-Transistor Logic (DTL) 11            |    |

|            | 1.8 Modified Diode-Transistor Logic 12         |    |

|            | 1.9 Transistor-Transistor Logic (TTL) 13       |    |

|            | 1.10 TTL Parameters 23                         |    |

|            | 1.11 Commonly Used ICs of Standard TTL 26      |    |

|            | 1.12 Improved TTL Series 27                    |    |

|            | 1.13 Comparison of TTL Families 29             |    |

|            | 1.14 Emitter Coupled Logic 29                  |    |

|            | 1.15 Integrated Injection Logic (I2L) 32       |    |

|            | 1.16 MOSFET Logic 34                           |    |

|            | 1.17 NMOS 34                                   |    |

|            | 1.18 CMOS 37                                   |    |

|            | 1.19 Comparison of CMOS and TTL Families 43    |    |

|            | 1.20 Interfacing CMOS and TTL Devices 43       |    |

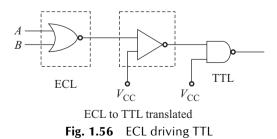

|            | 1.21 Interfacing ECL and TTL Devices 45        |    |

| Chapter 2: | NUMBER SYSTEM AND CODES                        | 51 |

|            | 2.1 Introduction 51                            |    |

|            | 2.2 Number Systems 51                          |    |

|            | 2.3 Interconversion of Numbers 53              |    |

|            | 2.4 Signed Binary Number 68                    |    |

|            | 2.5 Floating Point Representation of Number 76 |    |

|            | 2.6 Binary Arithmetic 77                       |    |

|            | 2.7 Complement Binary Arithmetic 81            |    |

- 2.8 Arithmetic Overflow 91

- 2.9 Codes 92

#### Chapter 3: BOOLEAN ALGEBRA AND LOGIC GATES 129

- 3.1 Introduction 129

- 3.2 Boolean Algebra 129

- 3.3 Overview of Logic Circuit 137

- 3.4 DeMorgan's Theorems 140

- 3.5 Standard Representation for Logical Functions 141

- 3.6 Minterm and Maxterm 142

- 3.7 Simplification of Boolean Expression 145

- 3.8 Simplification of Sum of Products 156

- 3.9 Simplification of Product of Sums 167

- 3.10 Don't-care Condition 178

- 3.11 Five- and Six-variables K-map 181

- 3.12 Quine-McCluskey Method 185

#### Chapter 4: COMBINATIONAL LOGIC CIRCUITS 198

- 4.1 Introduction 198

- 4.2 Design Procedure for Combinational Logic Circuit 198

- 4.3 Adders 202

- 4.4 Subtractor 211

- 4.5 BCD Adder 219

- 4.6 BCD Subtractor 220

- 4.7 Arithmetic Logic Unit 226

- 4.8 Comparator 229

- 4.9 Parity Generator 233

- 4.10 Parity Checker 235

- 4.11 Parity Generator/Checker (IC74180) 239

- 4.12 Multiplexer 241

- 4.13 Demultiplexer 257

- 4.14 Code Converters 264

- 4.15 PIN Diagrams of ICs 286

#### Chapter 5: SEQUENTIAL LOGIC CIRCUITS 293

- 5.1 Introduction 293

- 5.2 1-bit Memory Cell 294

- 5.3 Clocked S-R Flip-Flop 297

- 5.4 J-K Flip-Flop 299

- 5.5 D Flip-Flop 303

- 5.6 T Flip-Flop 303

- 5.7 Edge-Triggered Flip-Flop 304

- 5.8 Characteristics of Flip-Flop 306

- 5.9 Flip-Flop Conversions 307

- 5.10 Applications of Flip-Flops 323

- 5.11 Registers and Shift Registers 327

- 5.12 Applications of Shift Register 334

- 5.13 Commonly used ICs as Shift Register 341

- 5.14 Ripple Counter 343

- 5.15 Synchronous Counter 355

- 5.16 Flip-Flop Excitation Table 355

- 5.17 Synchronous Counter Design 358

- 5.18 UP/DOWN Counter 363

- 5.19 Clocked Sequential Circuit 369

- 5.20 Analysis of Clocked Sequential Circuit 371

- 5.21 Design of Clocked Sequential Circuit 375

- 5.22 Lockout Condition 398

- 5.23 Sequence Generator 401

- 5.24 Sequence Detector 406

#### Chapter 6: ASYNCHRONOUS SEQUENTIAL CIRCUITS 431

- 6.1 Introduction 431

- 6.2 Fundamental Mode Asynchronous Sequential Circuits 432

- 6.3 Pulse Mode Asynchronous Sequential Circuits 440

- 6.4 Incompletely Specified State Machines 447

- 6.5 Problems in Asynchronous Circuits 449

- 6.6 Design of Hazard-free Switching Circuits 452

#### Chapter 7: ALGORITHMIC STATE MACHINES 456

- 7.1 Introduction 456

- 7.2 Algorithmic State Machines 457

- 7.3 Realization of ASM Charts 464

- 7.4 Examples on ASM Charts 468

- 7.5 Register Transfer Language 478

- 7.6 RTL Notations 479

- 7.7 Data Unit Construction from an RTL Description 486

- 7.8 VHDL 491

#### Chapter 8: PROGRAMMABLE LOGIC DEVICES 529

- 8.1 Introduction 529

- 8.2 Programmable Logic Array 529

- 8.3 Programmable Array Logic 539

- 8.4 Generic Array Logic Devices 549

- 8.5 Classification of PLDs 550

- 8.6 Complex Programmable Logic Devices 551 8.7 Field Programmable Gate Array 555 8.8 Application Specific Integrated Circuits (ASICs) 561 Chapter 9: A/D AND D/A CONVERTERS 584 9.1 Introduction 584 9.2 Basic Principle of DAC 585 9.3 Basic Principle of ADC 596 9.4 DAC and ADC ICs 607 9.5 ADC 0809 (8-bit ADC) 608 9.6 ADC-7109 (12-bit binary ADC) 611 9.7 DAC 0808 (8-bit DAC) 626 SEMICONDUCTOR MEMORY DEVICES 630 Chapter 10: 10.1 Introduction 630 10.2 Memory Organization 630 10.3 Functional Diagram of Memory 631 10.4 Memory Operations 632 10.5 Expanding Memory Size 635 10.6 Characteristics of Memory Devices 641 10.7 Classification of Semiconductor Memories 642 10.8 Read and Write Memory 644

- 10.9 Read Only Memory 652

Index

664

# Chapter 1

# LOGIC FAMILIES

# Chapter Outline

- Types of logic families

- · Switching characteristics of transistor

- Characteristics of digital ICs

- RTL, DCTL, TTL, ECL logic families

- CMOS NAND, NOR and Inverter

- Comparison of TTL and CMOS

- Interfacing of TTL to CMOS and CMOS to TTL

- Interfacing of TTL to ECL and ECL to TTL

- 74XX series data sheet

# **1.1 INTRODUCTION**

Digital logic is concerned with the interconnection among digital components and modules. The best known example of a digital system is the general purpose digital computer. Most of the digital circuits are constructed on a single chip, which are referred to as *integrated circuits* (IC). Integrated circuits contain a large number of interconnected digital circuits within a single small package.

Small scale integration (SSI) and medium scale integration (MSI) devices provide digital functions and large scale integration (LSI) devices provide complete computer modules. It is very important for the logic designer to be familiar with the various digital components encountered in integrated circuit form. It is constructed by basic electronic components such as diodes, transistors, MOSFETs, registers, and capacitors. The complex digital functions can be realized using these basic electronic components in a variety of forms and each form is referred as a *logic family*.

Now-a-days digital integrated circuits are most commonly used in modern digital systems. ICs are popular due to their enormous advantages, as listed below.

- Small in size

- Low cost

- Less power consumption

- High noise margin

- High reliability

- High speed

This chapter includes the study of different logic families, interfacing of logic families, and data sheets of commonly used series 74XX.

# **1.2 LOGIC FAMILIES**

The set of compatible ICs with the same logic levels and same supply voltages have been fabricated to perform the various logic functions known as logic family. Based on the fabrication technology, logic families are classified into two types:

- Bipolar logic family

- Unipolar logic family

# Unipolar logic family

In unipolar logic families, unipolar devices are the key element. MOSFET (Metal Oxide Semiconductor Field Effect Transistor) is a unipolar device, in which the current flows because of only one type of charge carriers (that is, either electrons or holes). The examples of unipolar families include PMOS, NMOS, and CMOS.

# **Bipolar logic family**

Transistors and diodes are bipolar devices, in which the current flows because of both the charge carriers (electrons and holes). In bipolar logic families, transistors and diodes are used as key elements. On the basis of operations of transistors in ICs, bipolar logic families are further classified as:

- Saturated bipolar logic families

- Unsaturated bipolar logic families

In saturated bipolar logic families, transistors operate in saturation region. The speed of saturated bipolar logic family is low, reasons of which would be discussed in forthcoming topics. Examples of saturated bipolar logic families are:

- Resistor-transistor logic

- Direct coupled transistor logic

- Integrated injection logic

- Diode-transistor logic

- High-threshold logic

- Transistor-transistor logic

In non-saturated bipolar logic families, transistors operate in active region. The speed of non-saturated bipolar logic families is high as compared to saturated logic families. Examples of unsaturated bipolar logic families are:

- Schottky transistor-transistor logic

- Emitter-coupled logic

The transistor is one of the key elements used in logic families. One of the important applications of the transistor is the *switch*.

# **1.3 TRANSISTOR AS SWITCH**

Transistor is one of the basic elements of logic families. It operates as a switch. In switching circuits, transistors operate in cut-off or saturation region. The cut-off condition is referred to as *switch OFF* and saturation is referred to as *switch ON*.

In the cut-off region, both emitter and collector junctions are in reverse-bias condition and only reverse current flows in the transistor, which is negligible.

In the saturation region, both emitter and collector junctions are in forward bias condition. When transistor is operated in the saturation region, voltage across the emitter junction is  $V_{\text{BEsat}}$  and voltage across emitter and collector terminals is  $V_{\text{CEsat}}$ . The value of  $V_{\text{BEsat}} = 0.8$  V for silicon transistor and 0.3 V for germanium transistor. The value of  $V_{\text{CEsat}} = 0.2$  for silicon transistor and 0.1 V for germanium transistor. The condition to operate the transistor in saturation is that the base current should be greater than the collector current by  $\beta$ , that is,  $[I_B > I_C / \beta]$ .

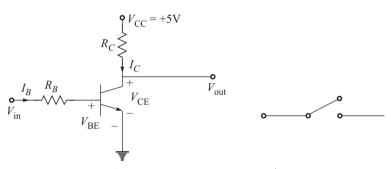

The circuit of a transistor working as a switch is shown in Fig. 1.1.

Fig. 1.1 Transistor as a switch

When input  $V_{in}$  applied to the transistor is LOW (0 V), the emitter junction is reverse biased, there is no current flowing through the base terminal and the current flowing through the collector terminal is reverse saturation current, which is negligible.

By applying KVL to the output loop,

$$V_{\rm CC} - I_C R_C - V_{\rm out} = 0$$

$$V_{\rm out} = V_{\rm CC} - I_C R_C$$

(1.1)

In the cut-off region, collector current  $I_C = 0$

$$V_{\rm out} = V_{\rm CC} \tag{1.2}$$

When the transistor is operating in cut-off, the output is equal to  $V_{CC}$  and it is referred to as HIGH (logic 1).

When input  $V_{in}$  that is applied to the transistor is HIGH (+5 V), the emitter junction is forward biased, current flowing through the base terminal is sufficient and the transistor operates in saturation region. Current flows through the collector terminal and there is a considerable voltage drop across the collector resistor. And output voltage is

$$V_{\rm out} = V_{\rm CEsat} \tag{1.3}$$

When the transistor is operating in saturation, the output is equal to  $V_{\text{CEsat}}$  and it is referred to as LOW (logic 0). Transistor is either ON or OFF and it is controlled by the input voltage.

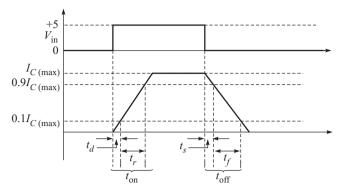

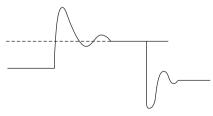

The response of a transistor switch for a square wave input is shown in Fig. 1.2.

Fig. 1.2 Response of transistor switch for square wave input

When a transistor switches from OFF to ON state, the charge built up requires time to reach the steady-state condition. Similarly when it switches from ON to OFF state, the excess charge stored must be removed which takes some time.

*Turn-ON time* It is the time required to reach the steady state condition when the input changes from low to high.

$$t_{\rm ON} = t_d + t_r \tag{1.4}$$

where  $t_d$  is delay time and  $t_r$  is rise time.

**Delay time** It is the time required for the collector current to rise from 0 to 10 percent of the maximum value of the collector current.

*Rise time* It is the time required for the collector current to rise from 10 to 90 percent of the maximum value of the collector current.

*Turn-OFF time* It is the time required to remove the excess charge stored near the junction, when the input changes from high to low.

$$t_{\rm OFF} = t_f + t_s \tag{1.5}$$

where  $t_f$  is fall time and  $t_s$  is storage time.

*Storage time* It is the time required to drop the collector current to 90 percent of the maximum value of the collector current when the input changes from high to low.

*Fall time* It is the time required to drop the collector current from 90 to 10 percent of the maximum value of the collector current.

# **1.4 CHARACTERISTICS OF DIGITAL ICs**

There are various logic families and the selection of a family for a particular application is based on its characteristics. Real time applications demand high speed logic families and hence it is necessary to study the characteristics of digital ICs. Following are the parameters used to compare the performance of digital ICs:

- Speed of operation

- Power dissipation

- Figure of merit

- Fan-out

- Fan-in

- Current and voltage parameters

- Noise Immunity

- Power supply requirements

- Operating temperature

# 1.4.1 Speed of Operation

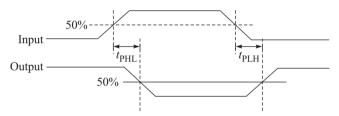

The speed of operation of digital ICs should be high. It is specified in terms of *propagation delay time*. It is the average of the propagation delay times from high to low state and low to high state.

$$t_p = \frac{t_{\text{PHL}} + t_{\text{PLH}}}{2} \tag{1.6}$$

where  $t_{PHL}$  is the delay time measured, when output changes from high to low state, and  $t_{PLH}$  is the delay time measured, when output changes from low to high state. The input and output voltage waveforms of a logic gate are shown in Fig. 1.3.

Fig. 1.3 Input and output voltage waveforms of logic gate

The delay times are measured between 50 percent voltage levels of input and output waveforms.

The propagation delay between input and output should be as minimum as possible so that the operating speed of IC remains high.

# 1.4.2 Power Dissipation

Every electronic circuit requires a certain amount of electric power for its operation. When the power is supplied by an external source, some of it is dissipated in electronic circuits. It is wastage of power across the circuit components and devices. Requirement of power is less, if the dissipation of power is less. Hence power dissipation should be as minimum as possible. Power dissipation of an IC is expressed in terms of milli Watt (mW).

# 1.4.3 Figure of Merit

The power dissipation of logic families should be minimum to reduce power requirements. But it is important to note that in logic families, if the power dissipation is reduced, the speed of operation gets reduced. Hence the *figure of merit* is a parameter considered for comparison instead of using the speed of operation and

power dissipation. Figure of merit is a product of propagation delay and power dissipation. It is measured in terms of Pico-Joules ( $ns \times mW = pJ$ ).

# 1.4.4 Current and Voltage Parameters

Current and voltage parameters define the minimum and maximum limit of current and voltage for input and output of a logic family.

$V_{IH}$  (*High level input voltage*) It is the minimum input voltage corresponding to logic 1 state.

$V_{IL}$  (Low level input voltage) It is the maximum input voltage corresponding to logic 0 state.

$V_{OH}$  (*High level output voltage*) It is the minimum output voltage corresponding to logic 1 state.

$V_{OL}$  (Low level output voltage) It is the maximum output voltage corresponding to logic 0 state.

$I_{IH}$  (*High level input current*) It is the minimum input current corresponding to logic 1 state.

$I_{IL}$  (Low level input current) It is the maximum input current corresponding to logic 0 state.

$I_{OH}$  (*High level output current*) It is the minimum output current corresponding to logic 1 state. This current is also referred to as the *source current*.

$I_{OL}$  (Low level output current) It is the maximum output current corresponding to logic 0 state. It is also referred to as the *sink current*.

# 1.4.5 Fan-Out

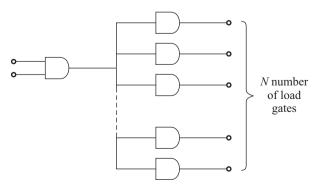

Fan-out is the capability of a logic gate to drive the maximum number of similar gates. High fan-out is advantageous, because it reduces the need of additional gates to drive more gates. Consider Fig.1.4.

In Fig. 1.4, the driver gate drives all the *N* gates (*N* is fan-out). If more than *N* gates are connected to a load of the driver gate, then the current supply by the driver gate is less than the current required to drive the gates, or the current sink by the driver gate is more than the rating of the driver gate which may damage the gate.

Fig. 1.4 AND gate driving *N* gates

The fan-out of a logic family can be calculated as

Fan-out = minimum of

$$\left\{ \frac{I_{\text{OH}}}{I_{\text{IH}}}, \frac{I_{\text{OL}}}{I_{\text{IL}}} \right\}$$

(1.7)

# 1.4.6 Fan-In

Fan-in is the number of inputs to a gate. For a two-inputs gate, fan-in is two; and for a four-inputs gate, fan-in is four.

#### 1.4.7 Noise Immunity

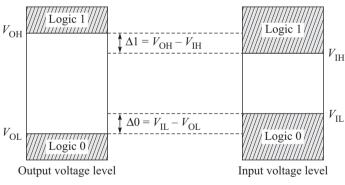

Unwanted signals are known as *noise*. The stray electric and magnetic fields may induce some noise at an input of digital circuit. Because of noise, the input voltage may drop below  $V_{\text{IH}}$  or may be raise above  $V_{\text{IL}}$ , which results in undesired operations. The circuit should have the ability to tolerate the noise signal. The noise immunity of digital circuit is defined as the ability of a digital circuit to tolerate the noise signal. A quantitative measure of noise immunity is known as *noise margin*. Logic 1 state noise margin and Logic 0 state noise margin can be calculated as:

Logic 1 state noise margin

$$\Delta 1 = V_{OH} - V_{IH}$$

(1.8)

Logic 0 state noise margin

$$\Delta 0 = V_{\rm IL} - V_{\rm OL}$$

(1.9)

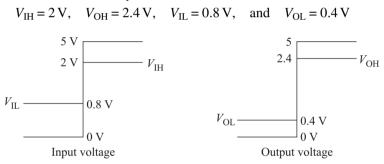

It is important that for logic families,  $V_{OH} > V_{IH}$  and  $V_{IL} > V_{OL}$  as shown in Fig. 1.5.

Fig. 1.5 Input and output voltage levels

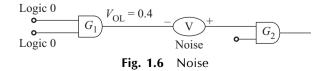

Let us see how the noise leads to an undesired output. Take the example of a TTL AND gate. A detailed study of TTL AND gate is covered in Section 1.9. The TTL gate has  $V_{\text{OH}} = 2.4 \text{ V}$ ,  $V_{\text{OL}} = 0.4 \text{ V}$ ,  $V_{\text{IH}} = 2 \text{ V}$ , and  $V_{\text{IL}} = 0.8 \text{ V}$ . The noise introduced in the signal ( $V_{\text{noise}}$ ) is shown in Fig. 1.6.

Let the inputs of gate<sub>1</sub> be such that the output of gate<sub>1</sub> is in logic 0 state  $(V_{OL} = 0.4 \text{ V})$ . This output is given as an input to gate<sub>2</sub>. Because of the noise present, the actual input given to gate<sub>2</sub> is:

$$V_{i2} = V_{OL} + V_{noise}$$

$$V_{i2} = 0.4 + V_{noise}$$

$$V_{noise} = V_{i2} - 0.4$$

$$(1.10)$$

The maximum low level input of the gate is 0.8 V. When the noise introduced in the signal is greater than (0.8 - 0.4) = 0.4 V, then the input to gate<sub>2</sub> will be greater than 0.8 V, which transits to an invalid input level and the output will be unpredictable.

Similarly for high state output of gate<sub>1</sub>

$$V_{i2} = 2.4 - V_{\text{noise}}$$

$$V_{\text{noise}} = 2.4 - V_{i2}$$

The minimum high level input of the gate is 2V. When the noise signal is greater than (2.4-2.0) = 0.4 V, the input of gate<sub>2</sub> will be less than 2V, which transits to an invalid input state and the output will be unpredictable.

# 1.4.8 Power Supply Requirements

Every electronic circuit requires supply voltage to operate. The required supply voltage and power by the IC should be as less as possible.

# 1.4.9 Operating Temperature

On the basis of operating temperature range, the application of the ICs will be decided. The operating temperature is the range of temperature in which an IC functions properly. It is in order of  $-55^{\circ}$ C to  $+125^{\circ}$ C. The accepted temperature range of an IC is 0 to  $+70^{\circ}$ C for commercial and industrial applications. Selection of a particular logic family for a particular application depends on these parameters. Let us learn each of these logic families.

# **1.5 RESISTOR-TRANSISTOR LOGIC (RTL)**

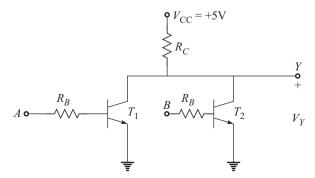

RTL consists of resistors and transistors. In RTL, transistors operate in cut-off region or saturation region as per the input voltage applied. Figure 1.7 shows the circuit of a two-inputs resistor-transistor logic NOR gate. Here *A* and *B* are the inputs of the gate and *Y* is the output.

Fig. 1.7 Resistor-transistor logic NOR gate

# Operation

- When the transistor operates in saturation region, maximum current flows through resistor  $R_C$ . The output voltage  $V_Y = V_{CEsat}$  ( $V_{CEsat} = 0.2$  V for silicon and 0.1 V for germanium); it is logic 0 level voltage. When the transistor operates in cut-off, no current flows through resistor  $R_C$  and the output voltage  $V_Y = V_{CC} = +5$  V; it is logic 1 level voltage.

- When both the inputs are in logic 0, transistors  $T_1$  and  $T_2$  operate in cut-off, and the output is  $+V_{CC}$ , i.e. +5 V (logic 1).

- When any one of the inputs is at logic 1 level, the corresponding transistor operates in saturation, and the output is  $V_Y = 0.2$  V (logic 0).

- When both the inputs are at logic 1 level, both the transistors operate in saturation and the output is  $V_Y = 0.2 \text{ V}$  (logic 0). The operation of circuit is summarized in Table 1.1(a).

| V <sub>A</sub> | V <sub>B</sub> | Transistor T <sub>1</sub> | Transistor T <sub>2</sub> | V <sub>Y</sub> |

|----------------|----------------|---------------------------|---------------------------|----------------|

| Logic 0        | Logic 0        | Cut-off                   | Cut-off                   | Logic 1        |

| Logic 0        | Logic 1        | Cut-off                   | Saturation                | Logic 0        |

| Logic 1        | Logic 0        | Saturation                | Cut-off                   | Logic 0        |

| Logic 1        | Logic 1        | Saturation                | Saturation                | Logic 0        |

Table 1.1(a)

Operation of RTL NOR gate (Fig. 1.7)

In terms of 0 and 1, the above table can be written as in Table 1.1(b).

| V <sub>B</sub> | V <sub>Y</sub> |

|----------------|----------------|

| 0              | 1              |

| 1              | 0              |

| 0              | 0              |

| 1              | 0              |

|                | 0              |

Table 1.1(b)Operation of RTL NOR gate (Fig. 1.7)

The circuit shown in Fig.1.7 acts as a two-inputs NOR gate and Table 1.1(b) is the truth table of NOR gate.

The RTL suffers from a few drawbacks as listed below:

- 1. Low noise margin (Typically 0.1 V)

- 2. Fan-out is poor (Typically 5)

- 3. Propagation delay is high and the speed of operation is low (Typically 12 ns)

- 4. High power dissipation (Typically 12 mW)

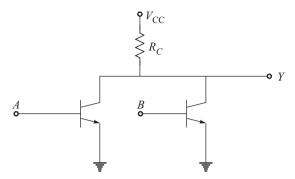

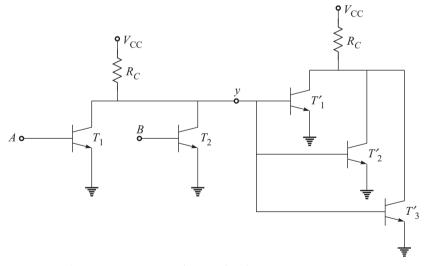

# **1.6 DIRECT COUPLED TRANSISTOR LOGIC (DCTL)**

In direct coupled transistor logic, the input signal is directly given to the base of the transistor. DCTL is simple than RTL. In DCTL, the transistor operates in saturation or cut-off region. Figure 1.8 shows the circuit of a two-inputs DCTL NOR gate.

Fig. 1.8 Two-inputs DCTL NOR gate

#### Operation

The operation of DCTL is same as the operation of RTL. When both the inputs are in logic 0, transistors operate in cut-off, and the output is logic 1. When any one of the inputs or both the inputs are in logic 1, the corresponding transistor or transistors operate in saturation and the output is logic 0.

Although DCTL is simpler than RTL, it is not popular because of the *current hogging problem*. Let us see what the current hogging problem is.

#### Current hogging problem

Figure 1.9 shows a DCTL gate driving a three-inputs NOR gate.

Fig. 1.9 DCTL gate driving the three-inputs NOR gate

Initially the input of transistor  $T_1$  is logic 0, and the input of transistor  $T_2$  is logic 1,  $T_1$  operates in cut-off and  $T_2$  operates in saturation, the output of driving gate is in logic 0 ( $V_{\text{CEsat}} = 0.2 \text{ V}$ ) which drives all the transistors in cut-off. When the input of  $T_2$  changes from logic 1 to logic 0,  $T_2$  operates in cut-off. The output of the driving gate starts to change from 0.2 V to  $V_{\text{CC}}$ .

Due to manufacturing tolerance, the base to emitter voltage of transistors  $T'_1$ ,  $T'_2$  and  $T'_3$  are different. Assume  $V_{\text{BEsat}}$  of transistors  $T'_1$ ,  $T'_2$  and  $T'_3$  are 0.8 V, 0.79 V and 0.78 V, respectively. When the voltage at the output of driving gate reaches 0.78 V,  $T'_3$  goes in saturation and will not allow other transistors to enter in saturation. The whole current flows through the base of  $T'_3$  and the transistors to enter in saturation. The whole current flows through the base of  $T'_3$  and the transistors to enter in saturation. The whole current flows through the base of  $T'_2$  and it may damage. Similarly, all the transistors of the driven circuit are damaged. It is known as the *current hogging problem*.

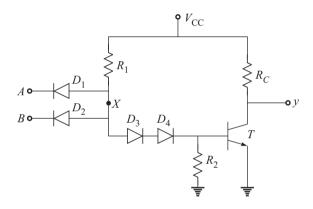

# 1.7 DIODE-TRANSISTOR LOGIC (DTL)

The circuit of a DTL consists of diodes and transistors. Figure 1.10 shows the circuit of a two-inputs diode-transistor logic NAND gate.

Fig. 1.10 Two-inputs DTL NAND gate

# Operation

- When the transistor operates in saturation, the output voltage  $V_{(0)} = V_{\text{CEsat}} = 0.2 \text{ V}$ ; and when it operates in cut-off, the output voltage  $V_{(1)} = V_{\text{CC}} = +5 \text{ V}$ .

- When both the inputs are in logic 0,  $V_{(0)} = V_{CEsat} = 0.2 \text{ V}$ , the input diodes are forward biased, voltage at point *x* is  $V_x = V_{(0)} + V_D = 0.2 + 0.7 = 0.9 \text{ V}$  which is not sufficient to drive the transistor in saturation, because the voltage desired at point *x* to drive the transistor in saturation should be  $V_{BEsat} + V_{D4} + V_{D3} = 0.8 + 0.7 + 0.9 = 2.2 \text{ V}$ . The transistor operates in cut-off and the output voltage is in logic 1 state.

- When any one of the inputs is in logic 1, the corresponding diode is forward biased. Voltage at point x is  $V_x = 0.2 \text{ V} + 0.7 \text{ V} = 0.9 \text{ V}$ ; the transistor operates in cut-off and the output voltage is in logic 1 state.

- When all the inputs are in logic 1 state, the diodes  $D_1$  and  $D_2$  are reverse biased. The resistances  $R_1$  and  $R_2$  are selected such that the transistor operates in saturation and the output voltage is in logic 0 state.

The operation of the circuit is summarized in Table 1.2(a).

| Inputs Dio |         | des            | Transistor            | output     |         |

|------------|---------|----------------|-----------------------|------------|---------|

| A          | В       | $D_1$          | <i>D</i> <sub>2</sub> | Т          | Y       |

| Logic 0    | Logic 0 | Forward biased | Forward biased        | Cut-off    | Logic 1 |

| Logic 0    | Logic 1 | Forward biased | Reverse biased        | Cut-off    | Logic 1 |

| Logic 1    | Logic 0 | Reverse biased | Forward biased        | Cut-off    | Logic 1 |

| Logic 1    | Logic 1 | Reverse biased | Reverse biased        | Saturation | Logic 0 |

Table 1.2(a)

Operation of DTL NAND gate (Fig. 1.10)

In terms of 0 and 1, Table 1.2(a) can be written as in Table 1.2(b).

| A | В | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Table 1.2(b)

Operation of DTL NAND gate (Fig. 1.10)

The circuit shown in Fig. 1.10 acts as a two-input NAND gate and Table1.2(b) shows the truth table of NAND gate.

Following are the advantages and disadvantages of DTL over RTL.

# Advantages

- 1. Fan-out is high.

- 2. Power dissipation is 8–12 mW.

- 3. Noise immunity is good.

#### Disadvantages

- 1. More elements are required.

- 2. Propagation delay is more (typically 30 ns) and hence the speed of operation is less.

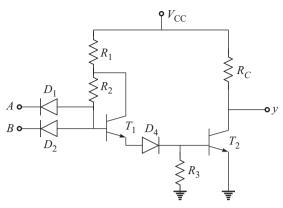

# **1.8 MODIFIED DIODE-TRANSISTOR LOGIC**

More fan-out gates are preferred for most of the applications. Fan-out of the gate is a function of source current. The fan-out of a logic gate is increased by increasing the current supply of the gate (source current). When the base current of a transistor is increased, then the source current in the diode-transistor logic increases and this in turn increases the fan-out. Replacement of the diode  $D_3$  in Fig. 1.10 by the transistor  $T_1$  increases the base current of the transistor and the circuit is referred as a modified diode-transistor logic. The modified diode-transistor logic has more fan-out as compared to DTL. The circuit diagram of a modified diode-transistor logic is shown in Fig. 1.11.

Fig. 1.11 Modified diode-transistor logic

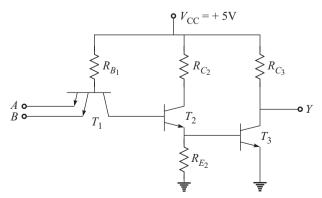

# **1.9 TRANSISTOR-TRANSISTOR LOGIC (TTL)**

Transistor-transistor logic is one of the popular saturated logic families. Transistor is the basic element of this logic family, which operates either in cut-off or saturation region. The first version of TTL is known as the standard TTL.

Standard TTLs are available in various forms:

- 1. TTL with passive pull-up

- 2. TTL with totem-pole output

- 3. TTL with open collector output

- 4. Tristate TTL

# 1.9.1 TTL with Passive Pull-Up

Figure 1.12 shows a two-input TTL NAND gate with passive pull-up. Transistor  $T_1$  has two emitter terminals. These terminals act as the inputs of the gate, that is, input *A* and input *B*. The input voltages are logic 0 or logic 1, where logic 0 corresponds to 0.2 V and logic 1 corresponds to +5 V.

Fig. 1.12 Two-input TTL NAND gate with passive pull-up

# Operation

- When both the inputs (A and B) are in logic 0,  $V_{(0)} = V_{\text{CEsat}} = 0.2 \text{ V}$ , the emitter junctions of transistor  $T_1$  are forward biased and the voltage at the base of transistor  $T_1$  is  $V_{\text{B1}} = V_{(0)} + V_{\text{BE}} = 0.2 + 0.7 = 0.9 \text{ V}$ . The minimum voltage required at the base of  $T_1$ , so that  $T_2$  and  $T_3$  start to conduct, is  $V_{\text{BEcut (in)}} + V_{\text{BEcut (in)}} + 0.7 = 0.5 + 0.5 + 0.7 = 1.7 \text{ V}$ . The required voltage is greater than the voltage available at the base of  $T_1$  and hence  $T_2$  and  $T_3$  are in cut-off and the output voltage is equal to the supply voltage  $V_{\text{CC}}$  (logic 1 level), output is in logic 1 state.

- When any one of the inputs is at logic 0 level, the corresponding emitter junction of  $T_1$  is forward biased and the voltage at the base of  $T_1$  is  $V_{B1} = V_{(0)} + V_{BE} = 0.2 + 0.7 = 0.9$  V. The minimum voltage required at the base of  $T_1$ , so that  $T_2$  and  $T_3$  start to conduct, is  $V_{BEcut (in)} + V_{BEcut (in)} + 0.7 = 0.5 + 0.5 + 0.7 = 1.7$  V. The required voltage is greater than the voltage available at the base of  $T_1$  and hence  $T_2$  and  $T_3$  are in cut-off and the output voltage is equal to the supply voltage  $V_{CC}$ , output is in logic 1 state.

- When all the inputs are in logic 1 state, the emitter junctions of  $T_1$  are reverse biased and the current supply by the source is sufficient to operate  $T_2$  and  $T_3$  in saturation and the output is in logic 0 state.

The operation of the circuit is summarized in Table 1.3(a).

| In      | puts    | Transistor T <sub>1</sub> |                | Transistors     | Output  |

|---------|---------|---------------------------|----------------|-----------------|---------|

| A       | В       | Emitter                   | Emitter        | $T_2$ and $T_3$ |         |

|         |         | junction A                | junction B     |                 |         |

| Logic 0 | Logic 0 | Forward biased            | Forward biased | Cut-off         | Logic 1 |

| Logic 0 | Logic 1 | Forward biased            | Reverse biased | Cut-off         | Logic 1 |

| Logic 1 | Logic 0 | Reverse biased            | Forward biased | Cut-off         | Logic 1 |

| Logic 1 | Logic 1 | Reverse biased            | Reverse biased | Saturation      | Logic 0 |

Table 1.3(a)

Operation of TTL NAND gate (Fig. 1.12)

In terms of 0 and 1, Table 1.3(a) can be written as follows:

| $V_A$ | V <sub>B</sub> | V <sub>Y</sub> |

|-------|----------------|----------------|

| 0     | 0              | 1              |

| 0     | 1              | 1              |

| 1     | 0              | 1              |

| 1     | 1              | 0              |

Table 1.3(b)

Operation of TTL NAND gate (Fig. 1.12)

The circuit shown in Fig. 1.12 acts as a two-input NAND gate and its truth table is given in Table 1.3(b).

# Passive pull-up

When both inputs are high,  $T_3$  operates in saturation region,  $V_0 = V_{\text{CEsat}}$  and the capacitor of loaded gate is charged up to  $V_{\text{CEsat}}$ . When one or more than one inputs change to logic 0, the corresponding emitter junction or junctions of  $T_1$  are forward biased and  $T_3$  goes into cut-off. The capacitor of the loaded gate starts charging towards  $V_{\text{CC}}$  through the resistor  $R_{C3}$  as shown in Fig. 1.13.

Fig. 1.13 TTL with passive pull-up

The capacitor of the loaded gate is pulled towards  $V_{CC}$  through the passive component  $R_{C_3}$  and hence the circuit is known as TTL with passive pull-up.

In TTL with passive pull-up, the time constant is  $R_{C_3} \times C_0$ . The speed of the circuit can be improved by decreasing  $R_{C_3}$ , which decreases the time constant. By decreasing the value of  $R_{C_3}$ , the power dissipation will go up due to the increased collector current of transistor  $T_3$ . This problem of TTL with passive pull-up is overcome in TTL with active pull-up.

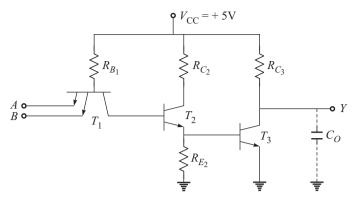

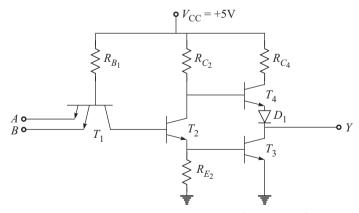

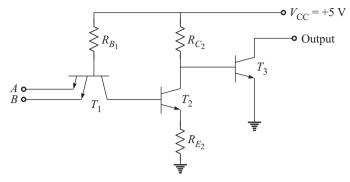

#### 1.9.2 TTL with Totem-Pole Output

Figure 1.14 shows the circuit of a two-input TTL NAND gate with totem-pole output. It is possible in TTL to improve the speed of operation by reducing the time constant without increasing power dissipation with the help of active pull-up. TTL with active pull-up is known as TTL with totem-pole output.

Fig. 1.14 Two-input TTL NAND gate with totem-pole output

#### Operation

• When both the inputs are in logic 0,  $V_{(0)} = V_{CEsat} = 0.2 \text{ V}$ , emitter junctions of  $T_1$  are forward biased and the voltage at the base of  $T_1$  is  $V_{B1} = V_{(0)} + V_{BE} = 0.2 + 0.7 = 0.9 \text{ V}$ . The minimum voltage required at the base of  $T_1$ , so that

$T_2$  and  $T_3$  start to conduct, is  $V_{\text{BEcut (in)}} + V_{\text{BEcut (in)}} + 0.7 = 0.5 + 0.5 + 0.7 = 1.7 \text{ V}$ . The required voltage is greater than the voltage available at the base of  $T_1$  and hence  $T_2$  and  $T_3$  are in cut-off and the output voltage is equal to the supply voltage  $V_{\text{CC}}$  (logic 1 level), output is in logic 1 state. Since  $T_2$  is in cut-off region, the current supply by the source  $V_{\text{CC}}$  through  $R_{C_2}$  is sufficient to operate  $T_4$  in saturation.

- When any one of the inputs is at logic 0 level, the corresponding emitter junction of  $T_1$  is forward biased and the voltage at the base of  $T_1$  is  $V_{B1} = V_{(0)} + V_{BE} = 0.2 + 0.7 = 0.9$  V. The minimum voltage required at the base of  $T_1$ , so that  $T_2$  and  $T_3$  start to conduct, is  $V_{BEcut (in)} + V_{BEcut (in)} + 0.7 = 0.5 + 0.5 + 0.7 = 1.7$  V. The required voltage is greater than the voltage available at the base of  $T_1$  and hence  $T_2$  and  $T_3$  are in cut-off and the output voltage is equal to the supply voltage  $V_{CC}$  (logic 1 level), output is in logic 1 state. Since  $T_2$  is uncertainty operator  $T_4$  in saturation.

- When all the inputs are in logic 1 state, the emitter junctions of  $T_1$  are reverse biased and the current supply by the source is sufficient to operate  $T_2$  and  $T_3$  in saturation and the output is logic 0 state. Since  $T_2$  is in saturation region, the voltage at the collector of  $T_2$  is low and  $T_4$  operates in cut-off.

The operation of the circuit is summarized in Table 1.4(a).

| Inputs  |         | Transistor T <sub>1</sub> |                       | Transistors     | Transistor | Output  |

|---------|---------|---------------------------|-----------------------|-----------------|------------|---------|

| A       | В       | Emitter<br>junction A     | Emitter<br>junction B | $T_2$ and $T_3$ | $T_4$      | Y       |

| Logic 0 | Logic 0 | Forward<br>biased         | Forward<br>biased     | Cut-off         | Saturation | Logic 1 |

| Logic 0 | Logic 1 | Forward<br>biased         | Reverse<br>biased     | Cut-off         | Saturation | Logic 1 |

| Logic 1 | Logic 0 | Reverse<br>biased         | Forward<br>biased     | Cut-off         | Saturation | Logic 1 |

| Logic 1 | Logic 1 | Reverse<br>biased         | Reverse<br>biased     | Saturation      | Cut-off    | Logic 0 |

Table 1.4(a)

Operation of TTL NAND gate (Fig. 1.14)

In terms of 0 and 1, Table 1.4(a) can be written as in Table 1.4(b).

| Table 1.4(b) | Operation of TTL NAND gate (Fig | g. 1.14) |

|--------------|---------------------------------|----------|

|--------------|---------------------------------|----------|

| A | В | Y |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

The circuit shown in Fig. 1.14 acts as a two-input NAND gate and its truth table is given in Table 1.4(b).

# Active pull-up

When both the inputs are high,  $T_3$  operates in saturation region,  $V_0 = V_{CEsat}$ , and  $T_4$  operates in cut-off. The current provided by the load is sinked by  $T_3$  and the capacitor of the loaded gate is charged up to  $V_{CEsat}$ .

When one or more than one input changes to logic 0, the corresponding emitter junction or junctions of  $T_1$  are forward biased.  $T_3$  goes into cut-off and  $T_4$  is in saturation and the diode  $D_1$  is forward biased. The capacitor of the loaded gate starts to charge towards  $V_{CC}$  through  $T_4$  and  $D_1$  as shown in Fig. 1.15.

The capacitor of the loaded gate is pulled towards  $V_{CC}$  through the active components  $T_4$  and  $D_1$ . Hence the circuit is known as TTL with active pull-up.

In totem-pole output,  $T_4$  acts as an emitter follower. The output impedance of emitter follower is low. This means that the output voltage can change quickly from low state to high state.

When the output changes from high to low,  $T_3$  operates in saturation and the capacitor of the loaded gate discharges quickly through  $T_3$ .

Due to the current spike problem, wired-AND connection must not be used for totem-pole output circuits, as discussed in the next section.

Fig. 1.15 Two-input TTL NAND gate totem-pole output with capacitive load

#### Function of diode in totem-pole output

In totem-pole output TTL, when  $T_3$  operates in saturation,  $T_4$  must operate in cutoff or vice versa. The diode  $D_1$  is used in the circuit to keep  $T_4$  in cut-off when the output is low. When  $T_2$  and  $T_3$  are in saturation, the voltage available at the base of  $T_4$  is

$$V_{B_4} = V_{\text{BE3sat}} + V_{\text{CE2sat}}$$

(1.11)

= 0.8 + 0.2 = 1 V

In the absence of a diode, the voltage required at the base of  $T_4$  so that it starts to conduct is

$$V_{B_4} = V_0 + V_{\text{BEcut (in)}}$$

(1.12)

= 0.2 + 0.5 = 0.7 V

The voltage available at the base of  $T_4$  is greater than the voltage required and hence both  $T_3$  and  $T_4$  are in saturation. To avoid this situation,  $D_1$  is used in the circuit.

In the presence of a diode, the voltage required at the base of  $T_4$ , for the transistor to conduct, is

$$V_{B_4} = V_{(O)} + V_D + V_{BEcut (in)}$$

(1.13)

= 0.2 + 0.7 + 0.5 = 1.4 V

The voltage available at the base of  $T_4$  is less than the voltage required and hence  $T_4$  is operating in cut-off.

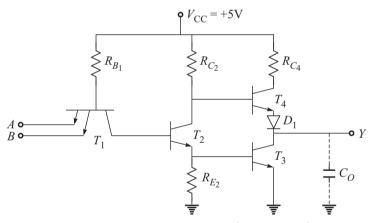

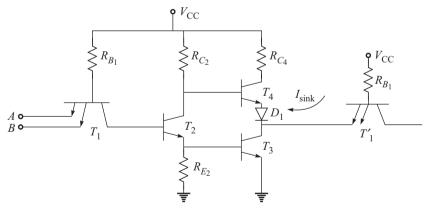

#### Sink current

It is the current supplied by the load. Figure 1.16 shows a two-input modified TTL NAND gate driving a similar gate.

When both the inputs are in logic 1 state,  $T_3$  operates in saturation and  $T_4$  is in cut-off. The output of the driver gate is logic 0 ( $V_0 = 0.2$  V), the emitter junction of transistor  $T'_1$  of the loaded gate becomes forward biased and the current supply by  $V_{CC}$  of the loaded gate passes through  $T_3$  of the driver gate. This current is known as the *sink current*.

Fig. 1.16 Two-input modified TTL NAND gate driving same gate

#### Source current

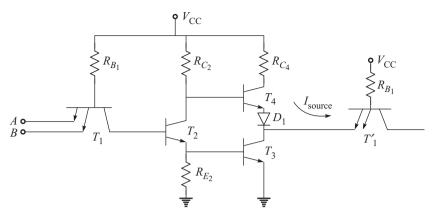

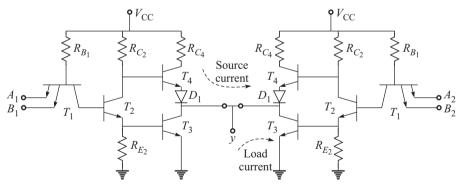

It is the current supplied by the driver gate to the loading gate(s). Figure 1.17 shows a two-input modified TTL NAND gate driving a similar gate.

When both or any one of the inputs is in logic 0 state,  $T_3$  operates in cut-off, and  $T_4$  is in saturation. The source  $V_{CC}$  supplies the current to the loading gate through  $R_{C_4}$ ,  $T_4$  and  $D_1$  as shown in Fig. 1.17. This current is known as the *source current*.

Fig. 1.17 Two-input modified TTL NAND

# **Clamped Diode**

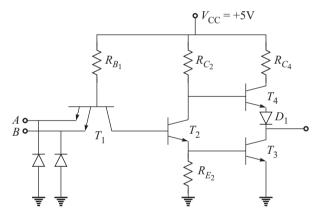

The circuit of a modified TTL with a clamping diode at input is shown in Fig. 1.18.

Fig. 1.18 Modified TTL with clamping diode at input

Clamping diodes are commonly used in TTL to suppress the *ringing* caused because of the fast transition found in TTL. At normal input signal, the diodes are reverse biased for high as well as low voltages. When transition occurs, the reactive component associated with the load causes ringing as shown in Fig. 1.19.

Fig. 1.19 Ringing effect

The rising on the positive side do not create any problem, but it makes the emitter junction reverse biased. Due to rising on the negative side, the emitter junction is more forward biased, the current flow through the emitter is very high, and the

transistor may be damaged. The diode(s) connected at the input is forward biased for negative spike and limits the voltage up to -0.7 V and protects the transistor.

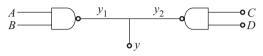

# 1.9.3 Wired-AND Connection

A wired-AND connection has two or more than two gates connected together. Using a wired-AND connection, the fan-in of the circuit is increased.

Fig. 1.20 Wired-AND connection

Here the outputs of two NAND gates are connected together.

$$Y = Y_1 \cdot Y_2$$

$$Y_1 = \overline{AB} \text{ and } Y_2 = \overline{CD}$$

Hence  $Y = \overline{AB} \cdot \overline{CD}$

Using De-Morgan's theorem,

$$Y = \overline{AB + CD} \tag{1.14}$$

Wired-AND connection is not possible in TTL with totem-pole output. The circuit diagram of a wired-AND connection for TTL with totem-pole output is shown in Fig. 1.21.

Fig. 1.21 Wired-AND connection for TTL with totem-pole output

When the output of gate<sub>1</sub> is high and gate<sub>2</sub> is low, then  $T_3$  of gate<sub>1</sub> operates in cut-off,  $T_4$  of gate<sub>1</sub> operates in saturation,  $T_3$  of gate<sub>2</sub> operates in saturation and  $T_4$  of gate<sub>2</sub> operates in cut-off. The load current and the current supplied by  $V_{CC}$  of gate<sub>1</sub> flow through  $T_3$  of gate<sub>2</sub> and  $T_3$  can be burnt out. Hence, wired-AND connection must not be used for totem-pole output TTL.

# 1.9.4 TTL with Open Collector Output

TTL with totem-pole output has a major problem that the two outputs of the two gates cannot be connected together. This problem of TTL with totem-pole output

is overcome in TTL with open collector output. Figure 1.22 shows the circuit of a TTL NAND gate with open collector output.

Fig. 1.22 TTL NAND gate with open collector output

The collector terminal of  $T_3$  is available outside the IC where the external resistor is to be connected. The circuit acts as a TTL with passive pull-up and hence the advantages of active pull-up cannot be achieved in the circuit but wired-AND connection is possible.

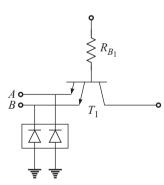

# 1.9.5 Unconnected Inputs of TTL

The input circuit of a TTL is shown in Fig. 1.23.

When the input is in logic 0 state, the emitter junction is forward biased and the current flows through the junction. When the input is in logic 1 state, the emitter junction is reversed biased and the current cannot flow through the junction. If any one of the inputs of the TTL gate is open, then the corresponding junction cannot be forward biased, and the current cannot flow. The input acts exactly in the same way, as in case when logic 1 is applied to that input. Therefore in TTL ICs, all unconnected inputs are treated as logical 1s.

Fig. 1.23 Input circuit of TTL

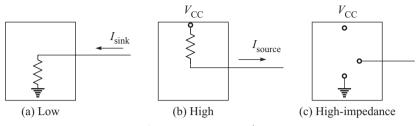

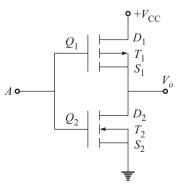

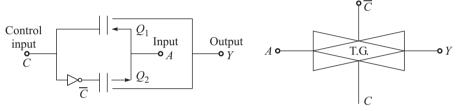

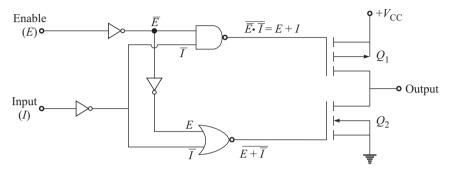

# 1.9.6 Tri-state TTL

A normal digital circuit has two output states: Low and High. The output is either in high state or low state. If the output is not in the low state, it is definitely in the high state. The tri-state TTL has three output states: High, Low, and Highimpedance.

In TTL with totem-pole output,  $T_3$  is ON when the output is low and  $T_4$  is ON when the output is high. In high-impedance state, both  $T_3$  and  $T_4$  in totem-pole arrangement are turned OFF and as a result, the output is open or floating.

When the output is low, the driver gate sinks the load current as shown in Fig. 1.24(a). When the output is high, the driver gate supplies the current to the

load as shown in Fig. 1.24(b). When the output is in high-impedance state, it acts as open or floating and there is no sink and source current as shown in Fig. 1.24(c).

Fig. 1.24 Tri-state logic

# Tri-state inverter

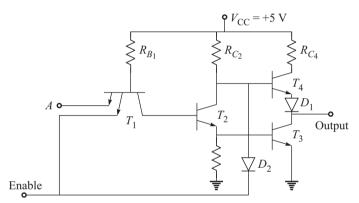

The circuit of a tri-state TTL inverter is shown in Fig. 1.25.

Fig. 1.25 Tri-state TTL inverter

The tri-state TTL inverter has two inputs—normal input A and enable input E.

- When the enable input E is High, the corresponding emitter junction of T<sub>1</sub> is reverse biased and the circuit operates as a normal inverter as explained below.

- When A is high, the second emitter junction of  $T_1$  is reverse biased. Current supplied by the source flows through the collector terminal of  $T_1$ , which forces  $T_2$  and  $T_3$  to be in saturation and the output is low.  $T_4$  operates in cut-off.

- When A is low, the corresponding emitter junction of  $T_1$  is forward biased, current supplied by the source flows through the emitter terminal of  $T_1$ , transistors  $T_2$  and  $T_3$  operate in cut-off and the output is high.  $T_4$  operates in ON state.

- When the enable input *E* is low, the corresponding emitter junction of  $T_1$  is forward biased. Current supplied by the source flows through the emitter terminal of  $T_1$ , transistors  $T_2$  and  $T_3$  operate in cut-off. Because of low enable input, the diode  $D_2$  is forward biased and the current supplied by the source flows through the diode  $D_2$ , transistor  $T_4$  is operated in cut-off and thus the output is in high-impedance state.

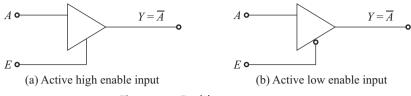

The logic symbols for the active high and active low enable input inverters are shown in Figs 1.26(a) and (b), respectively.

Fig. 1.26 Enable input inverter

# Application of tri-state logic

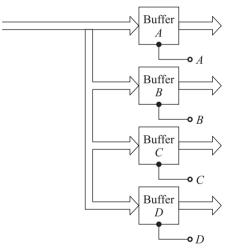

Tri-state buffers play an important role in computer systems. In case of 8085 microprocessor, all the buses are in tri-state whenever the 8085 is in reset mode.

Figure 1.27 shows the common bus connected to four output devices, where A, B, C and D are the enabled inputs of tri-state buffer. Data present over the bus is given to the device as per the enabled input signal of the tri-state buffer. The enabled signal of the input device is active low.

Fig. 1.27 Application of tri-state logic for data bus

When A = 0, B = 1, C = 1, D = 1, buffer A is enabled and others are disabled, and the data present over the line is given to device 1. When A = 1, B = 0, C = 1, D = 1, buffer B is enabled and others are disabled, and the data present over the line is given to device 2. When A = 1, B = 1, C = 0, D = 1, buffer C is enabled and others are disabled, and the data present over the line is given to device 3. When A = 1, B = 1, C = 1, D = 0, buffer D is enabled and others are disabled, and the data present over the line is given to device 4.

# **1.10 TTL PARAMETERS**

Now let us study the typical values of TTL family parameters.

# Speed of operation

The speed of operation of a TTL is specified in terms of propagation delay time. For a standard TTL, the propagation delay time is 18.5 ns.

If

$$t_{\text{PHL}} = 15$$

ns and  $t_{\text{PLH}} = 22$  ns, then  $t_p = \frac{15 + 22}{2} = 18.5$  ns

# Power dissipation

It signifies the wastage of power in a digital circuit. It should be as minimum as possible. For a standard TTL, power dissipation is 19 mW.

# Current and voltage parameters

$V_{\text{IH}}$ : It is the minimum input voltage to be recognized as logic 1 state.

$V_{\rm IL}$ : It is the maximum input voltage to be recognized as logic 0 state.

$V_{OH}$ : It is the minimum output voltage corresponding to logic 1 state

$V_{OL}$ : It is the maximum output voltage corresponding to logic 0 state.

For a standard TTL family:

Fig. 1.28 Voltage range for TTL

$I_{\rm IH}$ : It is the minimum input current corresponding to logic 1 state.

- $I_{\rm IL}$ : It is the maximum input current corresponding to logic 0 state

- $I_{OH}$ : It is the minimum output current corresponding to logic 1 state. It is called the *source current*.

- $I_{OL}$ : It is the maximum output current corresponding to logic 0 state. It is called the *sink current*.

For a standard TTL family:

$I_{\rm IH} = 40 \ \mu \text{A}, \quad I_{\rm OH} = -400 \ \mu \text{A}, \quad I_{\rm IL} = 1.6 \ \text{mA}, \text{ and } I_{\rm OL} = 16 \ \text{mA}$

# Fan-out

In digital applications, the output of a logic gate is given to one or more than one inputs of other logic gates. Fan-out is nothing but the capacity of the driver gate to drive a number of similar gates.

When the output of the driver gate is low,  $T_3$  sinks current from the forward biased emitter junction of transistor of the load as shown in Fig. 1.29(a). If *n* similar gates are connected at the output, then the total sink current  $I_{OL}$  is *n* times the input current  $I_{IL}$ , where *n* is the fan-out of TTL.

$I_{OL} = nI_{IL}$   $n = \frac{I_{OL}}{I_{IL}} = \frac{16 \text{ mA}}{1.6 \text{ mA}} = 10$   $P_{CC}$   $R_{C_4}$   $T_4$   $D_1$   $I_{OL}$   $T_2$   $T_3$   $T_{n-1}$   $T_{n-1}$

Fig. 1.29(a) TTL sinking the current from n gates

When the output of the driver gate is high,  $T_4$  acts as a current source to the load as shown in Fig. 1.29(b). If *n* similar gates are connected at the output, then the total source current must be equal to *n* times the input current  $I_{\text{IH}}$ , where *n* is the fan-out of TTL.

$$I_{OH} = n I_{IH}$$

$$n = \frac{I_{OH}}{I_{IH}} = \frac{400 \,\mu\text{A}}{40 \,\mu\text{A}} = 10$$

$$P_{CC}$$

$$R_{C_4}$$

$$T_4$$

$$D_1 I_{OH}$$

$$T_2$$

$$T_3$$

$$T_7$$

Fig. 1.29(b) TTL supplying the current to *n* gates

Fan-out = minimum of  $\left\{ \frac{I_{\text{OH}}}{I_{\text{IH}}}, \frac{I_{\text{OL}}}{I_{\text{IL}}} \right\}$

Fan-out for a standard TTL = minimum of  $\{10, 10\} = 10$

# Noise Margin

The noise immunity of a digital circuit is its ability to tolerate a noise signal. A quantitative measure of noise immunity is known as the *noise margin*.

Logic 1 level noise margin  $(\Delta 1) = V_{OH} - V_{IH}$

Logic 0 level noise margin ( $\Delta 0$ ) =  $V_{\rm IL} - V_{\rm OL}$

For a standard family,

$$V_{\rm IH} = 2 \text{ V}, \quad V_{\rm OH} = 2.4 \text{ V}, \quad V_{\rm IL} = 0.8 \text{ V}, \quad V_{\rm OL} = 0.4 \text{ V}$$

$$(\Delta 1) = 2.4 \text{ V} - 2 \text{ V} = 0.4 \text{ V} \qquad (\Delta 0) = 0.8 \text{ V} - 0.4 \text{ V} = 0.4 \text{ V}$$

# Supply voltage and temperature range

The 74 series and the 54 series are the examples of standard TTL logic families. These series operate on a power supply voltage of +5 V. But, it is found that the 74 series works reliably over the range +4.75 V to +5.25 V and the 54 series operates over the range +4.5 V to +5.25 V.

The 74 series can work reliably over a temperature range of  $0^{\circ}$ C to  $70^{\circ}$ C, while the 54 series can work over a temperature range of  $-55^{\circ}$ C to  $+125^{\circ}$ C.

# Summary of standard TTL

Table 1.5 summarizes the typical values of standard TTL parameters.

| Characteristics   | 74 series                                                 | 54 series                                                            |  |

|-------------------|-----------------------------------------------------------|----------------------------------------------------------------------|--|

| Supply voltage    | 4.75 V to 5.25 V                                          | 4.5 V to 5.5 V                                                       |  |

| Temperature range | $+0^{\circ}C$ to $70^{\circ}C$                            | – 55°C to 125°C                                                      |  |

| Voltage levels    | $V_{\rm IH} = 2 \text{ V}, V_{\rm OH} = 2.4 \text{ V}$    | $V_{\rm IH} = 2 \text{ V}, V_{\rm OH} = 2.4 \text{ V}$               |  |

|                   | $V_{\rm IL} = 0.8 \text{ V}, V_{\rm OL} = 0.4 \text{ V}$  | $V_{\rm IL} = 0.8 \text{ V}, V_{\rm OL} = 0.4 \text{ V}$             |  |

| Current levels    | $I_{\rm IH} = 40 \ \mu A, I_{\rm OH} = -400 \ \mu A$      | $I_{\rm IH} = 40 \ \mu \text{A}, \ I_{\rm OH} = -400 \ \mu \text{A}$ |  |

|                   | $I_{\rm IL} = 1.6 \text{ mA}, I_{\rm OL} = 16 \text{ mA}$ | $I_{\rm IL} = 1.6 \text{ mA}, \ I_{\rm OL} = 16 \text{ mA}$          |  |

| Power dissipation | 10 mW                                                     | 10 mW                                                                |  |

| Propagation delay | 10 ns                                                     | 10 ns                                                                |  |

| Fan-out           | 10                                                        | 10                                                                   |  |

| Noise margin      | 0.4 V                                                     | 0.4 V                                                                |  |

**Table 1.5**Typical values for standard TTL parameters

# **1.11 COMMONLY USED ICs OF STANDARD TTL**

Multiple emitter inputs and totem-pole output TTL circuits are used for different applications with a few exceptions. The 74 series is an example of a standard TTL family. It is available in different packages with different operations. The commonly used ICs of standard TTL are given in Table 1.6.

| IC number | Description                | IC number | Description               |

|-----------|----------------------------|-----------|---------------------------|

| 7400      | Quad 2-inputs NAND gates   | 7411      | Triple 3-inputs AND gates |

| 7402      | Quad 2-inputs NOR gates    | 7420      | Dual 4-inputs NAND gates  |

| 7404      | Hex Inverter               | 7424      | Dual 4-inputs AND gates   |

| 7408      | Quad 2-inputs AND gates    | 7432      | Quad 2-inputs OR gates    |

| 7410      | Triple 3-inputs NAND gates | 7486      | Quad 2-inputs EX-OR gates |

Table 1.6 Commonly used ICs of standard TTL

# **1.12 IMPROVED TTL SERIES**

TTL 54 series/74 series are the most popular and commonly used series of digital ICs. These series have the limitation of speed and power dissipation. These limitations are overcome up to a certain limit in the improved TTL series. The improved TTL series are as follows:

- 1. 74L series (low power TTL)

- 2. 74H series (high speed TTL)

- 3. 74S series (Schottky TTL)

- 4. 74LS series (low-power Schottky TTL)

- 5. 74AS series (advanced Schottky TTL)

- 6. 74ALS series (advanced low power Schottky TTL)

- 7. 74F series (fast TTL)

# 1.12.1 Low Power and High Speed TTL

The 74L series were developed to provide low power dissipation. The 74H series were developed to provide high speed. It is seen that the power dissipation goes down by increasing the charging resistance of the gate. Due to an increase in the value of the resistor, the delay is increased and the speed of operation is decreased. The 74L series has 1mW power dissipation and 33 ns propagation delay.

The speed of operation can be increased by reducing the value of the charging resistor. Due to low resistance, the power dissipation is increased. The high speed TTL, 74H series has 6 ns delay and 23 mW power dissipation.

The circuits of 74L series and 74H series are same as the circuit of a standard TTL, but they differ in circuit component values.

# 1.12.2 Schottky TTL

All the transistors in the circuits of standard TTL, low power TTL, and high speed TTL operate in saturation or cut-off region. When the transistor is in saturation, it stores the charge and the operation causes a storage-time delay during the transistor transition from ON to OFF; and this limits the circuit's switching speed.

In Schottky TTL families, Schottky transistors are used instead of normal transistors. The Schottky transistor is operated in active region or cut-off region, it never goes into saturation and the storage time delay is negligible.

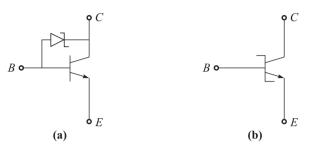

The Schottky transistor is obtained by using a Schottky barrier diode between the base and the collector terminals of the transistor as shown in Fig.1.30(a).

The Schottky diode has a forward biased voltage of 0.25 V. Because of this diode connected between the base and the collector terminals of the transistor, the collector junction of the transistor cannot get forward biased and the transistor never goes in saturation; the transistor operates in cut-off or active region. The symbol of Schottky transistor is shown in Fig. 1.30(b).

Fig. 1.30 Schottky transistor and Schottky symbol

The 74S series is an example of Schottky TTL. The propagation delay of Schottky TTL is 3 ns only, which is twice as fast as the 74H series. Figure 1.31 shows a basic NAND gate in Schottky TTL series.

Fig. 1.31 Schottky TTL NAND gate

# 1.12.3 Low Power Schottky TTL

The 74LS series is a low power Schottky TTL. It uses Schottky transistors. It is similar to 74S, but it has a large value of charging resistor than 74S series. The large resistor values reduce the circuit power requirement but increase the time delay. The 74LS series has 9.5 ns propagation delay and 2 mW power dissipation. The 74AS series is an advanced Schottky TTL. The 74ALS series is an advanced low power Schottky TTL and the 74F series is a fast TTL.

# **1.13 COMPARISON OF TTL FAMILIES**

A comparison of TTL families with respect to their common characteristics is given in Table 1.7.

| Character-<br>istics                  | 74        | 74 LS     | 74 S    | 74 ALS     | 74 AS    | 74 F       |

|---------------------------------------|-----------|-----------|---------|------------|----------|------------|

| Min. $V_{\rm OH}/V_{\rm OL}$          | 2.4/0.4   | 2.7/0.5   | 2.7/0.5 | 2.7/0.5    | 2.7/0.5  | 2.7/0.5    |

| Max. $V_{\rm IH}/V_{\rm IL}$          | 2/0.8     | 2/0.8     | 2/0.8   | 2/0.8      | 2/0.8    | 2/0.8      |

| Min. I <sub>OH</sub> /I <sub>OL</sub> | -0.4/16   | -0.4/16   | -1/20   | -0.4/16    | -2/20    | -1/20      |

| Max. I <sub>IH</sub> /I <sub>IL</sub> | 40/(-1.6) | 20/(-0.4) | 50/(-2) | 20/(- 0.2) | 0.2/(-2) | 20/(- 0.6) |

| $T_{\rm pd}(\rm ns)$                  | 10        | 10        | 3       | 4          | 1.5      | 2.5        |

| P.D. per gate<br>(mW)                 | 10        | 2         | 20      | 1          | 20       | 4          |

Table. 1.7 Comparison of TTL families

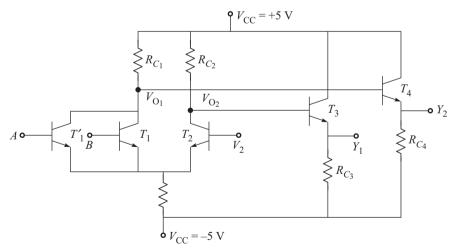

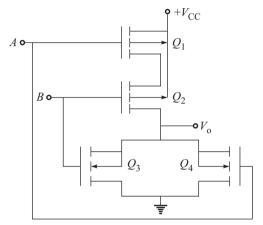

# **1.14 EMITTER COUPLED LOGIC**

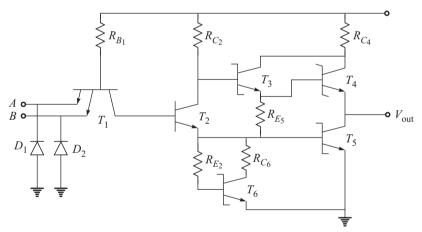

Emitter coupled logic (ECL) is faster than TTL family. The transistors of an emitter coupled logic are operated in cut-off or active region, it never goes in saturation and therefore the storage time is eliminated. Emitter coupled logic family is an example of unsaturated logic family. Figure 1.32 shows the circuit of an emitter-coupled logic OR/NOR gate.

Fig. 1.32 Emitter coupled logic OR/NOR gate

The circuit consists of difference amplifiers and emitter followers. Emitter terminals of the two transistors are connected together and hence it is called as emitter coupled logic.

The emitter followers are used at the output of difference amplifier to shift the DC level. The circuit has two outputs  $Y_1$  and  $Y_2$ , which are complementary.  $Y_1$  corresponds to OR logic and  $Y_2$  corresponds to NOR logic.

#### Operation

The input voltage of  $T_2$  is  $V_2 = V_{ref} = -1.15$  V.

- When both the inputs are in logic 0,  $T_1$  and  $T'_1$  operate in cut-off and  $T_2$  operates in active region, voltage  $V_{O_1}$  is high,  $T_3$  is ON, and the output at  $Y_2$  is logic 1, voltage  $V_{O_2}$  is low,  $T_4$  operates in cut-off and the output at  $Y_1$  is logic 0.

- When any one of the inputs is in logic 1 level, the corresponding transistors  $T_1$  or  $T'_1$  are operated in active region and  $T_2$  operates in cut-off, voltage  $V_{O_1}$  is low,  $T_3$  operates in cut-off and  $Y_2$  is logic 0, voltage  $V_{O_2}$  is high,  $T_4$  operates in active region and  $Y_1$  is logic 1.

- When both the inputs are in logic 1 state,  $T_1$  and  $T'_1$  operate in active region and  $T_2$  operates in cut-off, voltage  $V_{O_1}$  is low,  $T_3$  operates in cut-off and  $Y_2$ is logic 0, voltage  $V_{O_2}$  is high,  $T_4$  operates in active region and  $Y_1$  is logic 1.

The operation of the circuit is summarized in Table 1.8(a).

| Inputs  |         | Transistors |          |                       | Transistors           |         | Output                |                       |

|---------|---------|-------------|----------|-----------------------|-----------------------|---------|-----------------------|-----------------------|

| A       | В       | $T_{I}$     | $T'_{1}$ | <i>T</i> <sub>2</sub> | <i>T</i> <sub>3</sub> | $T_4$   | <i>Y</i> <sub>1</sub> | <i>Y</i> <sub>2</sub> |

| Logic 0 | Logic 0 | Cut-off     | Cut-off  | Active                | Active                | Cut-off | Logic 0               | Logic 1               |

| Logic 0 | Logic 1 | Cut-off     | Active   | Cut-off               | Cut-off               | Active  | Logic 1               | Logic 0               |

| Logic 1 | Logic 0 | Active      | Cut-off  | Cut-off               | Cut-off               | Active  | Logic 1               | Logic 0               |

| Logic 1 | Logic 1 | Active      | Active   | Cut-off               | Cut-off               | Active  | Logic 1               | Logic 0               |

Table 1.8(a) Operation of ECL circuit

In terms of 0 and 1, Table 1.8(a) can be written as in Table 1.8(b).

Table 1.8(b) Operation of ECL circuit

|   | A | В | Y <sub>1</sub> | <i>Y</i> <sub>2</sub> | W(OD)                           |

|---|---|---|----------------|-----------------------|---------------------------------|

| Γ | 0 | 0 | 0              | 1                     | A o Y(OR)                       |

|   | 0 | 1 | 1              | 0                     | $B \bullet \overline{Y}(NOR)$   |

|   | 1 | 0 | 1              | 0                     | <b>00</b>                       |

|   | 1 | 1 | 1              | 0                     | Fig. 1.33 Symbol of OR/NOR gate |

The circuit shown in Fig.1.32 acts as a two-input OR/NOR gate and its truth table is given in Table 1.8(b). The symbol of emitter coupled logic OR / NOR gate is shown in Fig.1.33.

# Fan-out

Fan-out of logic families is a function of current supply by the source and the input current of individual loaded gates. These are functions of the input and output resistances of the logic family. If the input resistance of a loaded gate is high, then the required current is less. If the output resistance is low, then the supply current is more. For emitter coupled logic, the transistor is used in the emitter follower mode due to which the input resistance is high and the output resistance is low. Thus, current supply by the driving gate is more and the current required to drive the individual gate is less and therefore the fan-out is large.

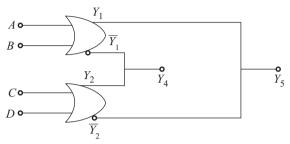

# Wired-OR logic

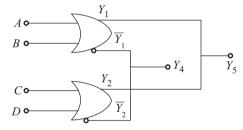

The ECL circuit has two outputs  $Y_1$  and  $Y_2$ .  $Y_1$  is the output of OR logic and  $Y_2$  is the output of NOR logic.  $(Y_1 = A + B, Y_2 = \overline{Y} = \overline{A + B})$ . When the outputs of two or more than two gates are connected, then an additional logic is realized without using any additional hardware. Consider the circuit shown in Fig. 1.34.

Fig. 1.34 Wired-OR logic

$$Y_4 = \overline{Y_1} + Y_2 = \overline{A} \quad \overline{B} + C + D$$

$$Y_5 = Y_1 + \overline{Y_2} = A + B + \overline{C + D}$$

Consider another circuit shown in Fig. 1.35.

Fig. 1.35 Wired-OR logic

$$Y_4 = \overline{Y_1} + \overline{Y_2} = \overline{A + B} + \overline{C + D}$$

$$Y_5 = Y_1 + Y_2 = A + B + C + D$$

(1.15)

# Unconnected inputs

If any one of the inputs of the ECL gate is open, then the corresponding transistor operates in cut-off and there is no current flow through the transistor. The same condition occurs when the input is in logic 0 level and hence the unconnected input of ECL is treated as logic 0.

# ECL characteristics

Following are the characteristics of an ECL circuit:

- 1. Less propagation delay time ( $t_d = 1$  ns).

- 2. The logic low-level voltage is -1.7 V and the logic high level voltage is -0.8 V.

- 3. Poor noise margin.

- 4. Power dissipation within the range of 40–55 mW.

- 5. Fan-out is 25.

## 1.15 INTEGRATED INJECTION LOGIC $(I^2L)$

The integrated injection logic uses only transistors for the construction of a gate and hence it becomes possible to integrate a large number of gates in a single package. This IC is easier and cheaper to fabricate. The figure of merit of  $I^2L$  circuits is quite small (4 PJ).

## 1.15.1 *I*<sup>2</sup>*L* Inverter

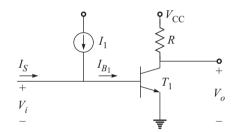

Figure 1.36 shows a simple inverter circuit. If the input  $V_1$  is at low logic level, transistor  $T_1$  is off and  $I_{B_1} = 0$ .

The input source acts as a sink for the current supplied by the current source  $I_1$  and the output is at high logic level. If the input is high, the base current  $I_{B_1} = I_S + I_1$  and  $T_1$  operates in saturation. The output is at low logic level.

**Fig. 1.36** *I*<sup>2</sup>*L* Inverter with current source

Figure 1.37 shows a simple inverter circuit with transistor  $T_2$  as the constant current source, hence  $T_2$  is in series as a constant current source.

**Fig. 1.37** *I*<sup>2</sup>*L* Inverter with transistor as current source

When the input is low, the source sinks the current and  $T_1$  is off and the output is high. When the input is high, the base current of  $T_1$  is the sum of currents  $I_1$  and the current supplied by the source,  $T_1$  is ON and the output is low.

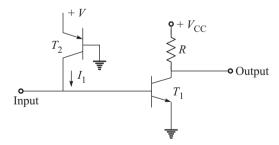

Figure 1.38 shows the  $I^2L$  inverter circuit with two output terminals. Transistor  $T_1$  has two collector terminals. The outputs are connected directly to the inputs of other  $I^2L$  gate.

**Fig. 1.38**  $l^2L$  inverter circuit with two output terminals

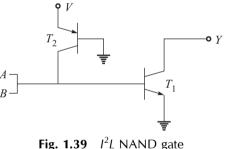

# 1.15.2 *I*<sup>2</sup>*L* NAND Gate

Figure 1.39 shows the  $I^2L$  NAND gate. When inputs A and B are low or any one of the inputs is low, the current provided by  $T_2$  is sinked by the source,  $T_1$  is OFF, and the output is high. When both the inputs are high, the base current of  $T_1$  is the sum of currents provided by the source and  $T_2$ , transistor  $T_1$  is ON and the output is low.

Table 1.9Truth Table of NOR gate

| Inputs |   | Output |

|--------|---|--------|

| A      | В | Y      |

| 0      | 0 | 1      |

| 0      | 1 | 1      |

| 1      | 1 | 1      |

| 1      | 1 | 0      |

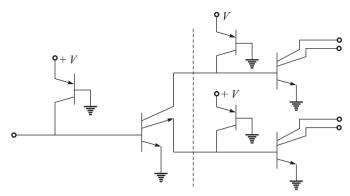

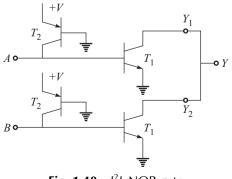

## 1.15.3 *I*<sup>2</sup>*L* NOR Gate

Figure 1.40 shows the  $l^2L$  NOR gate. The circuit has two inverters with their outputs connected together. When both or any one of the inputs is high, the output of the corresponding inverter is low and the resulting output is low.

When both inputs are low, the output of both the inverters is high and the result is also high.

| Inpu | Inputs |                | Outputs               |   | Outputs |  |

|------|--------|----------------|-----------------------|---|---------|--|

| A    | B      | Y <sub>1</sub> | <i>Y</i> <sub>2</sub> |   |         |  |

| 0    | 0      | 1              | 1                     | 1 |         |  |

| 0    | 1      | 1              | 0                     | 0 |         |  |

| 1    | 0      | 0              | 1                     | 0 |         |  |

| 1    | 1      | 0              | 0                     | 0 |         |  |

**Fig. 1.40** *I*<sup>2</sup>*L* NOR gate

## 1.16 MOSFET LOGIC

MOSFETs are very popular due to their low power dissipation and high density of fabrication. The logic families of MOSFETs can be classified into three categories: (i) PMOS, (ii) NMOS, and (iii) CMOS.

PMOS logic is slow as compared to NMOS logic. Hence, it is not used in new designs.

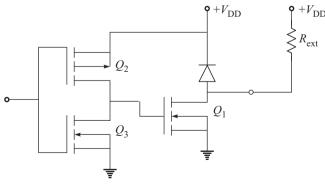

## 1.17 NMOS

MOSFETs are of two types—*depletion type* and *enhancement type*. NMOS family uses only *n*-channel enhancement MOSFETs.

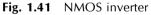

#### 1.17.1 NMOS Inverter

Figure 1.41 shows the circuit of an NMOS inverter consisting of *n*-channel MOSFETs. When the drain and gate terminals of MOSFETs are short-circuited, then it acts as a resistor.

In Fig. 1.41, MOSFET  $Q_1$  acts as a load resistor and MOSFET  $Q_2$  acts as a switching element.  $Q_1$  is always ON; the load resistance is equal to  $R_{ON}$  of the *n*-channel MOSFET. Instead of load resistance,  $Q_1$  is used, which reduces the size of the chip.  $Q_1$  may be of depletion type or enhancement type. But  $Q_2$  is always of enhancement type.

#### Operation

- When the input signal is high (positive voltage), Q<sub>2</sub> is ON, the current flows through the drain terminal and the output is low.

- When the input signal is low (0 V or negative voltage), Q<sub>2</sub> is OFF, there is no current flow through the circuit and the output is high (V<sub>DD</sub>).

The operation of the circuit is summarized in Table 1.11 (a). In terms of 0 and 1, we can write it as in

Table 1.11(b). The circuit in Fig. 1.41 acts as a NOT gate and its truth table is given in Table 1.11(b).

| Table | 1.11 (a) | Operation of |

|-------|----------|--------------|

|       | NMOS ir  | nverter      |

| Vin   | $Q_2$ | Vo                  |

|-------|-------|---------------------|

| 0 V   | OFF   | $V_{\rm DD}$ = +5 V |

| + 5 V | ON    | 0 V                 |

| Table | 1.11 (b) | Operation of |

|-------|----------|--------------|

|       | NMOS ir  | nverter      |

| V <sub>in</sub> | V <sub>0</sub> |

|-----------------|----------------|

| 0               | 1              |

| 1               | 0              |

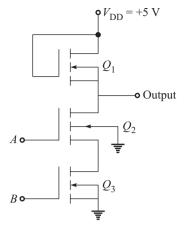

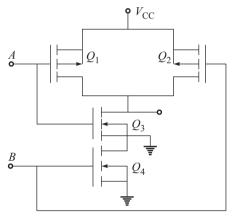

## 1.17.2 NMOS NAND Gate

Similar to NMOS inverter,  $Q_1$  acts as a load resistor that reduces the size of the chip; and here  $Q_1$  is always ON.  $Q_2$  and  $Q_3$  are the switching elements. These two

switching elements are connected in series, which are controlled by the inputs A and B.  $Q_1$ may be of depletion type or enhancement type, but  $Q_2$  and  $Q_3$  are always enhancement MOSFETs.

#### Operation

- When both of the inputs are low,  $Q_2$  and  $Q_3$  are OFF, the current cannot flow through the drain terminal and the output is high ( $V_{\text{DD}}$ ).

- When any one of the inputs is low (0V or negative), then the corresponding MOSFET is OFF. There is no current flow through the circuit and the output is high (V<sub>DD</sub>).

Fig. 1.42 A two-input NAND gate using NMOS

When inputs are high (+ve voltage), Q<sub>2</sub> and Q<sub>3</sub> are ON. The current flows through the drain terminal and the output is low.

The operation of the circuit is summarized in Table 1.12(a).

| A    | B    | $Q_2$ | $Q_3$ | Vo   |

|------|------|-------|-------|------|

| LOW  | LOW  | OFF   | OFF   | HIGH |

| LOW  | HIGH | OFF   | ON    | HIGH |

| HIGH | LOW  | ON    | OFF   | HIGH |

| HIGH | HIGH | ON    | ON    | LOW  |

Table 1.12(a) Operation of NMOS NAND gate

In terms of 0 and 1, Table 1.12(a) can be written as in Table 1.12(b).

Table 1.12(b) Operation of NMOS NAND gate

| A | В | V <sub>0</sub> |

|---|---|----------------|

| 0 | 0 | 1              |

| 0 | 1 | 1              |

| 1 | 0 | 1              |

| 1 | 1 | 0              |

The circuit shown in Fig.1.42 acts as a two-input NAND gate and its truth table is given in Table 1.12(b).

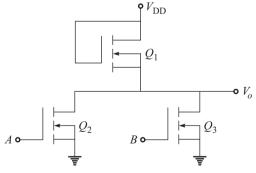

## 1.17.3 NMOS NOR Gate

Figure 1.43 shows a two-input NMOS gate.  $Q_1$  acts as a load resistor. It is always ON. MOSFETs  $Q_2$  and  $Q_3$  are the switching elements. These switching elements are connected in parallel, which are controlled by inputs A and B. Instead of load resistance,  $Q_1$  is used which reduces the size of the chip.  $Q_1$  may be of depletion type or enhancement type, but  $Q_2$  and  $Q_3$  are always enhancement MOSFETs.

#### Operation

- When both the inputs are low,  $Q_2$  and  $Q_3$  are OFF. The current cannot flow through the drain terminal and the output is high  $(V_{DD})$ .

- When any one of the inputs is high (0 V or -ve), then the corresponding MOSFET is ON. The current flows through the circuit and the output is low.

- When inputs are high (+ve voltage),  $Q_2$  and  $Q_3$  are ON. The current flows through the drain terminal and the output is low.

The operation of the circuit is summarized in Table 1.13(a).

| A    | В    | $Q_2$ | $Q_3$ | Vo   |

|------|------|-------|-------|------|

| LOW  | LOW  | OFF   | OFF   | HIGH |

| LOW  | HIGH | OFF   | ON    | LOW  |

| HIGH | LOW  | ON    | OFF   | LOW  |

| HIGH | HIGH | ON    | ON    | LOW  |

Table 1.13(a) NMOS NOR gate

In terms of 0 and 1, Table 1.13(a) can be written as in Table 1.13(b).

| A | В | $V_o$ |  |  |

|---|---|-------|--|--|

| 0 | 0 | 1     |  |  |

| 0 | 1 | 0     |  |  |

| 1 | 0 | 0     |  |  |

| 1 | 1 | 0     |  |  |

Table 1.13(b) NMOS NOR gate

The circuit shown in Fig. 1.43 acts as a two-inputs NAND gate and its truth table is given in Table 1.13(b).

Fig. 1.43 NMOS NOR gate

## 1.17.4 Fan-out

We have seen that the fan-out of a logic family is the function of its input and output impedance. For high input impedance, the fan-out is large. MOSFET devices have very high input impedance, therefore fan-out is large. Since the number of driving gates is more, the capacitor at the driving gate output considerably reduces the speed of MOSFET gate.

## 1.17.5 Propagation Delay Time

It is a function of the capacitor of loaded gate and the charging resistor. In case of MOS devices, the large capacitor is present at input and output and the resistor through which the capacitor gets charged or discharged is also high. Hence, the propagation delay is large and the speed of operation is low.

## 1.17.6 Power Dissipation

It is a function of current supply by the source and resistance of the load. The power supply by the source in MOS logic family is small and hence the power dissipation is low.

## 1.17.7 Characteristics of NMOS

Table 1.14 summarizes the characteristics of NMOS.

| Parameter       | Value  | Parameter       | Value    | Parameter        | Value  |

|-----------------|--------|-----------------|----------|------------------|--------|

| V <sub>IH</sub> | 2.0 V  | I <sub>OH</sub> | – 400 µA | t <sub>PHL</sub> | 60 ns  |

| $V_{\rm IL}$    | 0.8 V  | I <sub>OL</sub> | 2 mA     | t <sub>PLH</sub> | 45 ns  |

| V <sub>OH</sub> | 2.4 V  | Fan-out         | 30       | P.D.             | 0.1 mW |

| V <sub>OL</sub> | 0.45 V | Noise margin    | 1.5 V    |                  |        |

Table 1.14

Characteristics of NMOS

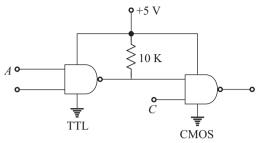

## 1.18 CMOS

CMOS family uses *n*-channel and *p*-channel MOSFETs. In CMOS, *p*-channel and *n*-channel MOS devices are fabricated on the same chip, which makes its fabrication complicated but it reduces the packaging density, and has small power consumption. Hence, CMOS is ideally suited for battery-operated systems.

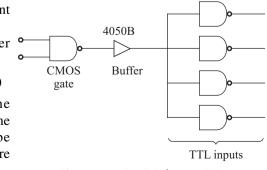

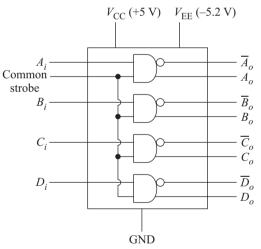

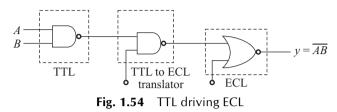

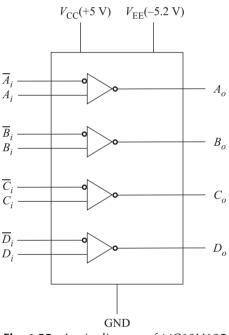

## 1.18.1 CMOS Inverter